DS04-24500-2E

# ASSP Single-chip Demodulator for Digital Satellite Broadcasting

## **MB86660A**

#### DESCRIPTION

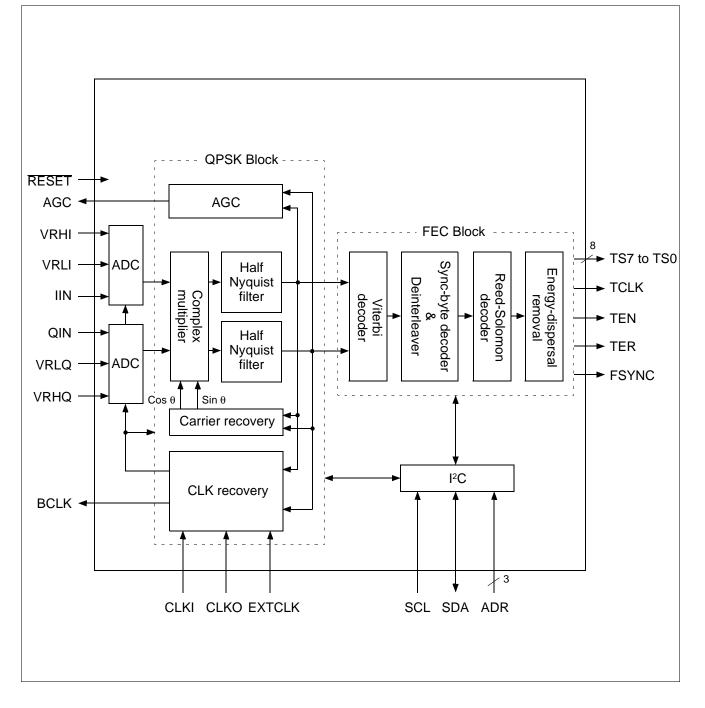

MB86660A is a single-chip demodulator for digital satellite broadcasting, and is compatible for DVB-S and DSS\*. It consists of two A/D converters for I-input and Q-input, QPSK demodulator and forward-error correction (FEC) unit which has Viterbi decoder and Reed-Solomon decoder.

#### ■ FEATURES

- DVB-S and DSS\* compatible single-chip demodulator

- Operation rate up to 62 Mbps

- A/D converters for I-input and Q-input Analog 1 V p-p and up to 31 Msymbol/s input

- QPSK demodulator Gray-coded QPSK demodulation with absolute mapping On-chip multi-rate VCO (36 to 62 MHz operation) Automatic carrier capture range = ±5 MHz Half Nyquist filters roll-off factor α = 0.35 Automatic gain control (AGC): PWM output

(Continued)

- Viterbi decoder

Constraint length K = 7

Viterbi rate R = 1/2, 2/3, 3/4, 5/6, 7/8

- Reed-Solomon decoder n = 204, k = 188, t = 8

- Deinterleaver: depth I = 12

- Energy-dispersal removal: PRBS polynomial =  $x^{15} + x^{14} + 1$

- C/N monitoring output via I<sup>2</sup>C interface

- I<sup>2</sup>C bus interface

- Power supply voltage: +3.3 V

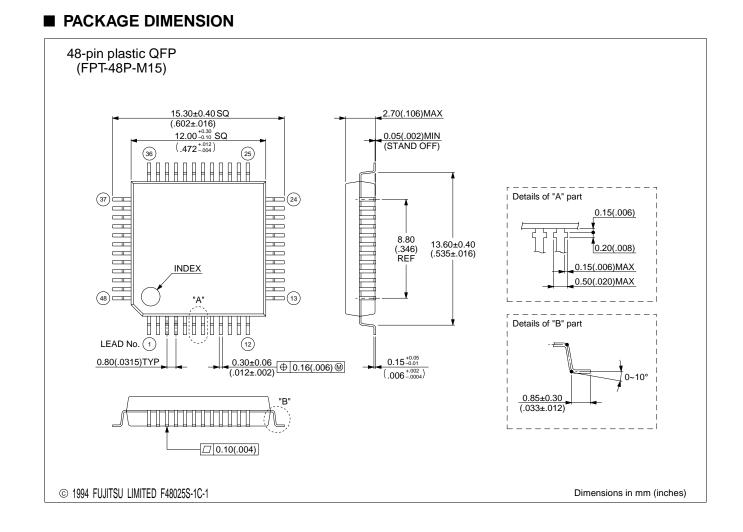

- Package: QFP-48

- Process: 0.35 μm CMOS

#### \*: For detailed information on DSS usage, please contact your nearest Fujitsu.

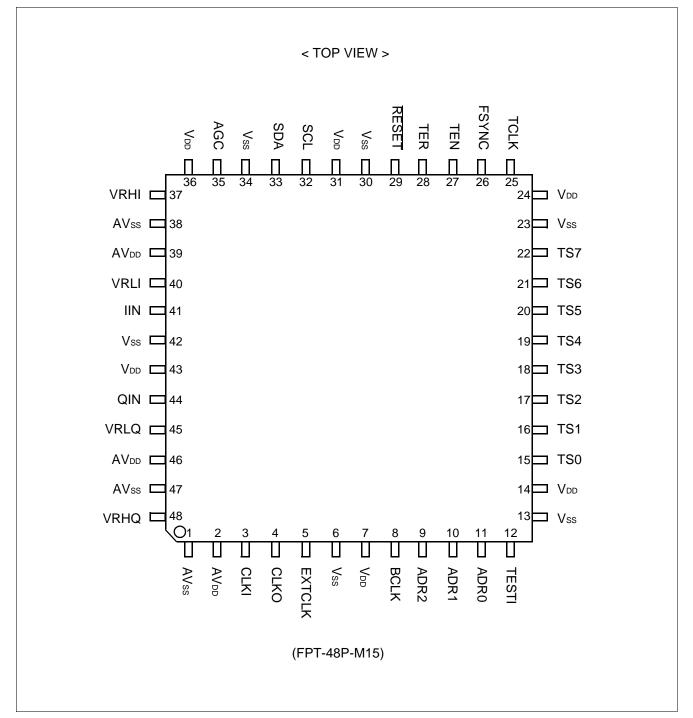

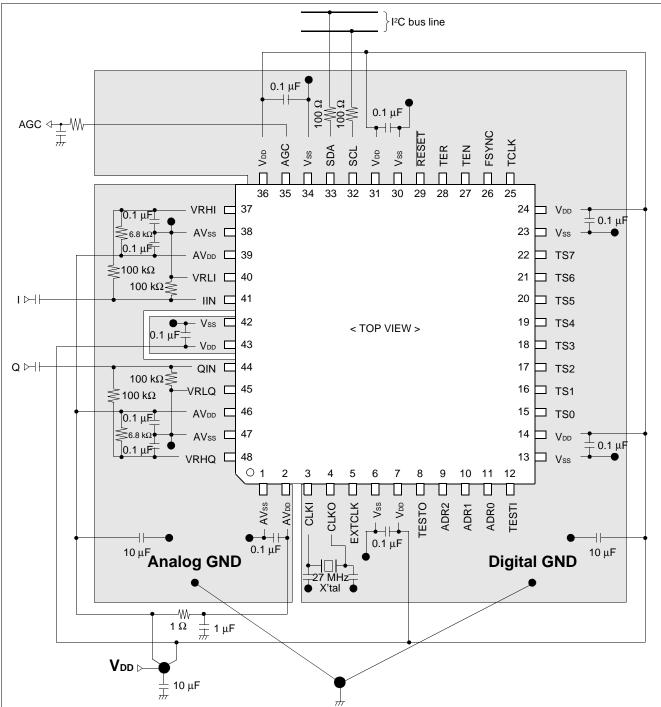

#### PIN ASSIGNMENT

#### ■ PIN DESCRIPTION

| Pin no.  | Symbol       | Pin name                            | I/O      | Function                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|--------------|-------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 41       | IIN          | QPSK analog<br>I-input              | I        | <b>QPSK analog in-phase input:</b><br>Analog 1 V p-p input. The maximum input rate is 31<br>Msymbol/s.                                                                                                                                                                                                                                                                                                              |

| 44       | QIN          | QPSK analog<br>Q-input              | I        | <b>QPSK analog quadrature-phase input:</b><br>Analog 1 V p-p input. The maximum input rate is 31<br>Msymbol/s.                                                                                                                                                                                                                                                                                                      |

| 37       | VRHI         | A/D high reference                  | I        | <b>A/D high reference input for IIN:</b><br>High reference voltage input. The typical voltage is 1.4 V.                                                                                                                                                                                                                                                                                                             |

| 40       | VRLI         | A/D low<br>reference                | I        | <b>A/D low reference input for IIN:</b><br>Low reference voltage input. The typical voltage is 0 V.                                                                                                                                                                                                                                                                                                                 |

| 48       | VRHQ         | A/D high reference                  | I        | <b>A/D high reference input for QIN:</b><br>High reference voltage input. The typical voltage is 1.4 V.                                                                                                                                                                                                                                                                                                             |

| 45       | VRLQ         | A/D low<br>reference                | I        | <b>A/D low reference input for QIN:</b><br>Low reference voltage input. The typical voltage is 0 V.                                                                                                                                                                                                                                                                                                                 |

| 35       | AGC          | AGC output                          | 0        | <b>AGC output:</b><br>PWM (Pulse Width Modulation) or 'H/L' level output. This<br>output pin is fed to an external analog filter that controls an<br>AGC amplifier of the tuner.                                                                                                                                                                                                                                    |

| 3<br>4   | CLKI<br>CLKO | Crystal<br>oscillator input         | I<br>I/O | <b>Crystal oscillator input:</b><br>Connect a 27.0 MHz crystal oscillator between these pins.<br>It is used to set the frequency of internal multi-rate VCO.<br>This crystal oscillator is not required when the EXTCLK pin<br>inputs 27.0 MHz clock.<br>When the crystal oscillator is not used, CLKI and CLKO<br>must be 'L' and 'OPEN' respectively. When the crystal<br>oscillator is used, EXTCLK must be 'L'. |

| 5        | EXTCLK       | External clock<br>input             | I        | <b>External clock input:</b><br>This pin inputs 27.0 MHz clock to set the frequency of internal multi-rate VCO. The crystal oscillator is not required when this pin is used. When this EXTCLK is not used, it must be 'L'.                                                                                                                                                                                         |

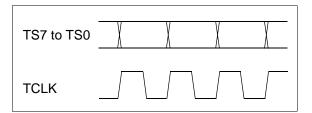

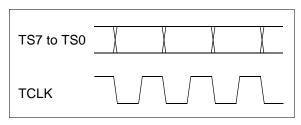

| 22 to 15 | TS7 to TS0   | Transport<br>packet data<br>output  | 0        | <b>Transport data output:</b><br>These pins are the transport stream packet data. User can select the output mode, either from 8-bit parallel data or serial data output. When parallel output, user can select MSB position, TS7 or TS0. When serial output, user can select the output pin position, TS0 or TS7. All selections are done by setting the register.                                                 |

| 25       | TCLK         | Transport<br>packet clock<br>output | 0        | <b>Transport clock output:</b><br>This pin is the transport stream packet clock for TS7 to TS0. User can select the output mode that is parallel or serial clock, and select the clock polarity. All selections are done by setting the register.                                                                                                                                                                   |

| 27       | TEN          | Transport<br>packet enable          | 0        | <b>Transport enable output:</b><br>This pin outputs 'H' during the valid data of the packet, and outputs 'L' during the others such as the parity byte.                                                                                                                                                                                                                                                             |

| Pin no.                  | Symbol               | Pin name                        | I/O | Function                                                                                                                                                                                                                                            |

|--------------------------|----------------------|---------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28                       | TER                  | Error indicator                 | 0   | <b>Error indicator output:</b><br>This pin outputs 'H' for a period of a packet that the Reed-<br>Solomon decoder could not correct, and outputs 'L' for a<br>period of a packet that it could correct.                                             |

| 26                       | FSYNC                | Frame<br>synchronous<br>output  | 0   | <b>Frame synchronous output:</b><br>This pin outputs 'H' when the frame is synchronized.                                                                                                                                                            |

| 32                       | SCL                  | I <sup>2</sup> C bus clock      | Ι   | Serial clock input for I <sup>2</sup> C bus                                                                                                                                                                                                         |

| 33                       | SDA                  | I <sup>2</sup> C bus data       | I/O | Serial data I/O for I <sup>2</sup> C bus                                                                                                                                                                                                            |

| 9<br>10<br>11            | ADR2<br>ADR1<br>ADR0 | l <sup>2</sup> C bus<br>address | Ι   | Address ID input for I <sup>2</sup> C bus:<br>These are the lower 3-bit of I <sup>2</sup> C bus address. The upper<br>4-bit is fixed with "0001".                                                                                                   |

| 29                       | RESET                | Reset input                     | I   | Reset input:<br>The MB86660A is reset when this pin inputs 'L'. The LSI<br>must be reset when the power is turned on. Refer to<br>■ Power-on Reset in detail.                                                                                       |

| 8                        | BCLK                 | Bit clock<br>output             | Ο   | <b>Bit clock output:</b><br>This pin can output the twice clock for the symbol rate, the same clock for the symbol rate, or the packet start signal.<br>All selections are done by setting the register. This pin outputs 'L' at the initial stage. |

| 12                       | TESTI                | Test pin                        | Ι   | Test pin:<br>This input test pin must be connected to 'L'.                                                                                                                                                                                          |

| 39, 46, 2                | AVdd                 | Analog Vod                      | _   | Analog $V_{DD}$ :<br>Analog $V_{DD}$ for the internal A/Ds and VCO.                                                                                                                                                                                 |

| 38, 47, 1                | AVss                 | Analog Vss                      | _   | Analog Vss:<br>Analog GND for the internal A/Ds and VCO.                                                                                                                                                                                            |

| 7, 14, 24,<br>31, 36, 43 | Vdd                  | Digital VDD                     | _   | Digital VDD                                                                                                                                                                                                                                         |

| 6, 13, 23,<br>30, 34, 42 | Vss                  | Digital Vss                     | _   | Digital V <sub>ss</sub>                                                                                                                                                                                                                             |

#### BLOCK DIAGRAM

#### ABSOLUTE MAXIMUM RATINGS (See WARNING)

| Parameter            | Symbol    | Rat  | ing       | Unit |  |

|----------------------|-----------|------|-----------|------|--|

| Farameter            | Symbol    | Min. | Max.      | Onit |  |

| Power supply voltage | Vdd, AVdd | -0.5 | +4.0      | V    |  |

| Input voltage        | Vı        | -0.5 | Vdd + 0.5 | V    |  |

| Output voltage       | Vo        | -0.5 | Vdd + 0.5 | V    |  |

| Storage temperature  | Тѕт       | -55  | +125      | °C   |  |

**WARNING:** Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### RECOMMENDED OPERATING CONDITIONS

| Parameter                | Symbol    |                            | Unit     |                            |      |  |

|--------------------------|-----------|----------------------------|----------|----------------------------|------|--|

| Falameter                | Symbol    | Min.                       | Тур.     | Max.                       | Onit |  |

| Power supply voltage     | Vdd, AVdd | 3.0                        | 3.3      | 3.6                        | V    |  |

| High level input voltage | Vін       | $V_{\text{DD}} 	imes 0.65$ | —        | Vdd + 0.3                  | V    |  |

| Low level input voltage  | VIL       | -0.3                       |          | $V_{\text{DD}} 	imes 0.25$ | V    |  |

| Operating temperature    | Та        |                            | 0 to +70 |                            | °C   |  |

**WARNING:** Recommended operating conditions are normal operating ranges for the semiconductor device. All the device's electrical characteristics are warranted when operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representative beforehand.

#### ■ ELECTRICAL CHARACTERISTICS

#### **DC Characteristics**

| $(V_{DD} = +3.3 \pm 0.3 \text{ V}, \text{ Ta} = 0 \text{ to } +70^{\circ}\text{C} \text{ unless otherwise specified}$ |              |                                                     |                             |                |                             |      |  |

|-----------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------|-----------------------------|----------------|-----------------------------|------|--|

| Parameter                                                                                                             | Symbol       | Conditions                                          |                             | Value          |                             | Unit |  |

| Falameter                                                                                                             | Symbol       | Conditions                                          | Min.                        | <b>Typ.</b> *1 | Max.                        | Unit |  |

| Logic input                                                                                                           |              |                                                     |                             |                |                             |      |  |

| Input high voltage                                                                                                    | Vін          | _                                                   | $V_{\text{DD}} \times 0.65$ | —              | Vdd + 0.3                   | V    |  |

| Input low voltage                                                                                                     | VIL          | _                                                   | -0.3                        | _              | $V_{\text{DD}} \times 0.25$ | V    |  |

| I <sup>2</sup> C bus input (SDA and SCL)                                                                              | 1            | 1                                                   |                             |                |                             |      |  |

| Input high voltage                                                                                                    | VIH          |                                                     | 3.0                         | _              | 5.5                         | V    |  |

| Input low voltage                                                                                                     | VIL          |                                                     | -0.5                        |                | 1.5                         | V    |  |

| A/D input (VRHI, VRHQ, VRLI, V                                                                                        | /RLQ, IIN an | d QIN)                                              |                             |                |                             |      |  |

| Input reference high voltage<br>(for VRHI and VRHQ)                                                                   | Vrh          | _                                                   | V <sub>RL</sub> + 1.0       | 1.4            | Vdd                         | V    |  |

| Input reference low voltage<br>(for VRLI and VRLQ)                                                                    | Vrl          | _                                                   | 0                           | 0              | Vrн – 1.0                   | V    |  |

| Differential reference voltage                                                                                        | Vrw          | Vrh – Vrl                                           | 1.0                         | 1.4            | 2.5                         | V    |  |

| Reference input resistance                                                                                            | Rrw          | VRH to VRL                                          | _                           | 5              | _                           | kΩ   |  |

| Analog input voltage<br>(for IIN and QIN)                                                                             | Vi           | _                                                   | Vrl                         |                | Vrh                         | V    |  |

| Analog input capacitance<br>(for IIN and QIN)                                                                         | Cin          | _                                                   | _                           | 15             | _                           | pF   |  |

| Logic output                                                                                                          | l            |                                                     |                             |                |                             |      |  |

| Output high voltage                                                                                                   | Vон          | Iон = -4 mA                                         | Vdd - 0.5                   | _              | _                           | V    |  |

| Output low voltage                                                                                                    | Vol          | lo∟ = 4 mA                                          | _                           | _              | 0.4                         | V    |  |

| I <sup>2</sup> C bus output (SDA)                                                                                     |              |                                                     | - L                         |                |                             |      |  |

| Output low voltage                                                                                                    | Vol          | lo∟ = 3 mA                                          | _                           | _              | 0.4                         | V    |  |

| Power supply current (VDD and A                                                                                       | Vdd)         |                                                     |                             |                |                             |      |  |

| Average power supply current                                                                                          | lod          | IIN, QIN =<br>31 Mbaud/s<br>V <sub>DD</sub> = 3.6 V | _                           | 300            | T.B.D.                      | mA   |  |

\*1: Typical values assume that  $V_{DD}$  = +3.3 V and Ta = +25°C.

#### REGISTER TABLE

#### 1. Register Map

C address:

0

0

0

1

ADR2

ADR1

ADR0

>

| Register                                       |             | Register                            | (MSB)                 | Bit function     |                       |                       |                  |                  |                  |                       |

|------------------------------------------------|-------------|-------------------------------------|-----------------------|------------------|-----------------------|-----------------------|------------------|------------------|------------------|-----------------------|

| address                                        | Access      | name                                | bit 7                 | bit 6            | bit 5                 | bit 4                 | bit 3            | bit 2            | bit 1            | bit 0                 |

| 00000000<br>(0)                                | R/W         | MODE-1                              | MOD7<br>(0)           | Reserved<br>(0)  | MOD5<br>(0)           | MOD4<br>(0)           | MOD3<br>(0)      | MOD2<br>(0)      | MOD1<br>(0)      | MOD0<br>(0)           |

| 00000001 (1)                                   | R/W         | MODE-2                              | Reserved<br>(0)       | Reserved<br>(0)  | Reserved<br>(0)       | BCLK1<br>(0)          | BCLK0<br>(0)     | ER_EN<br>(1)     | RS_EN<br>(1)     | DI_EN<br>(1)          |

| 00000010<br>(2)                                | R/W         | AGC                                 | Reserved<br>(0)       | AGCP<br>(0)      | AGCM<br>(0)           | AGC4<br>(1)           | AGC3<br>(0)      | AGC2<br>(0)      | AGC1<br>(0)      | AGC0<br>(0)           |

| 00000011<br>(3)                                | R/W         | VCO                                 | VCO7<br>(0)           | VCO6<br>(0)      | VCO5<br>(0)           | VCO4<br>(1)           | VCO3<br>(0)      | VCO2<br>(1)      | VCO1<br>(1)      | VCO0<br>(0)           |

| 00000100<br>(4)                                | R/W         | Viterbi<br>VCO<br>Expansion         | LVCO<br>(0)           | 0                | 0                     | VIR4<br>(0)           | VIR3<br>(0)      | VIR2<br>(1)      | VIR1<br>(0)      | VIR0<br>(0)           |

| 00000101<br>(5)                                | R/W         | Frame Sync.                         | SYT3<br>(1)           | SYT2<br>(1)      | SYT1<br>(1)           | SYT0<br>(1)           | SYA3<br>(0)      | SYA2<br>(0)      | SYA1<br>(1)      | SYA0<br>(0)           |

| 00000110<br>(6)                                | R/W         | Carrier Recovery loop filter Coeff. | CA_SW<br>(1)          | CA_β2<br>(0)     | CA_β1<br>(1)          | CA_β0<br>(0)          | 0                | CA_α2<br>(0)     | CA_α1<br>(0)     | CA_α0<br>(1)          |

| 00000111<br>(7)                                | R/W         | Clock Recovery loop filter Coeff.   | 0                     | CL_β2<br>(0)     | CL_β1<br>(1)          | CL_β0<br>(1)          | 0                | CL_α2<br>(0)     | CL_α1<br>(1)     | CL_α0<br>(0)          |

| 00001000<br>(8)                                | W           | RESET                               | X<br>(0)              | X<br>(0)         | X<br>(0)              | X<br>(0)              | X<br>(0)         | X<br>(0)         | QP_RST<br>(0)    | LSI_RST<br>(0)        |

| 00001001<br>(9)                                | R           | Status                              | Х                     | х                | х                     | STA4                  | STA3             | STA2             | STA1             | STA0                  |

| 00001010<br>(10)                               | R           | AFC                                 | AFC7                  | AFC6             | AFC5                  | AFC4                  | AFC3             | AFC2             | AFC1             | AFC0                  |

| 00001011<br>(11)                               | R           | C/N                                 | CN7                   | CN6              | CN5                   | CN4                   | CN3              | CN2              | CN1              | CN0                   |

| 00001100<br>(12)<br>•<br>•<br>00010000<br>(16) | •<br>•<br>• | Reserved<br>•<br>•<br>Reserved      | X<br>•<br>•<br>*<br>X | ×<br>•<br>•<br>× | X<br>•<br>•<br>*<br>X | X<br>•<br>•<br>*<br>X | ×<br>•<br>•<br>× | ×<br>•<br>•<br>× | ×<br>•<br>•<br>× | X<br>•<br>•<br>*<br>* |

| 00010001<br>(17)                               | R/W         | Start Carrier<br>Coeff.             | X<br>(0)              | CAS_β2<br>(0)    | CAS_β1<br>(1)         | CAS_β0<br>(1)         | X<br>(0)         | CAS_α2<br>(0)    | CAS_α1<br>(1)    | CAS_α0<br>(1)         |

| 00010010<br>(18)                               | R           | Unused                              | 1                     | 1                | 1                     | 1                     | 1                | 1                | 1                | 1                     |

| 00010011<br>(19)                               | R/W         | AGC<br>Coefficiency                 | X<br>(0)              | AGC_β2<br>(0)    | AGC_β1<br>(0)         | AGC_β0<br>(0)         | X<br>(0)         | AGC_α2<br>(0)    | AGC_α1<br>(1)    | AGC_α0<br>(1)         |

Note: X: Don't care.

(0) or (1): Initial value

#### ■ FUNCTIONAL DESCRIPTION

#### 1. MODE-1

- User can select the output polarity of TCLK, the output mode of TS7 to TS0 and so on by setting the register.

- Register value: I<sup>2</sup>C address = 0001ADR [2:0], Register address = 00000000 (2)

| Bit name | Function           | Bit value   | Operation                                                                                                                        |

|----------|--------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------|

| MOD0     | TCLK polarity      | 0 (initial) | TS7 to TS0 are latched at the falling edge of the TCLK.                                                                          |

|          |                    | 1           | TS7 to TS0 are latched at the rising edge of the TCLK.                                                                           |

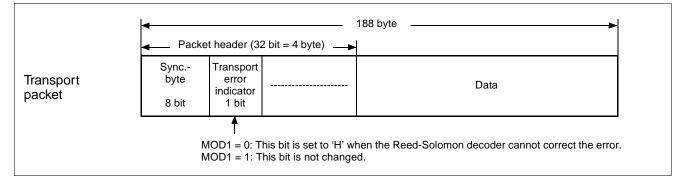

| MOD1     | Error indicator    | 0 (initial) | The error indicator flag of the transport stream packet is set to<br>'H' when the Reed-Solomon decoder cannot correct the error. |

|          |                    | 1           | The error indicator flag of the transport stream packet is not changed.                                                          |

| MOD2     | Output mode of     | 0 (initial) | Parallel output.                                                                                                                 |

|          | TS7 to TS0         | 1           | Serial output. Another TS bits output 'L'.                                                                                       |

| MOD3     | Output order of    | 0 (initial) | TS7 is MSB when parallel. TS0 outputs when serial.                                                                               |

|          | TS7 to TS0         | 1           | TS0 is MSB when parallel. TS7 outputs when serial.                                                                               |

| MOD4     | FSYNC output       | 0 (initial) | FSYNC outputs the frame synchronous signal.                                                                                      |

|          | mode               | 1           | FSYNC outputs the Viterbi synchronous signal.                                                                                    |

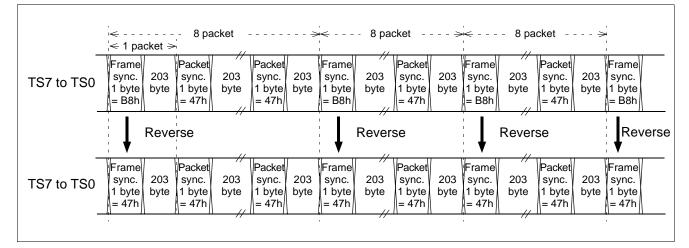

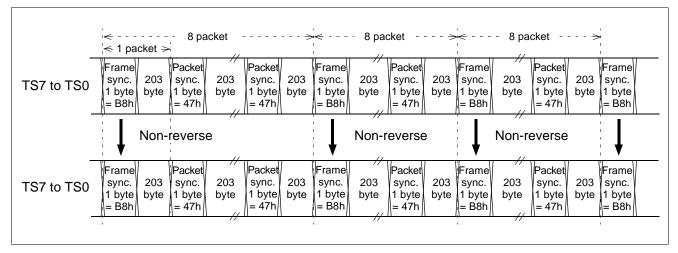

| MOD5     | Frame<br>sync-mode | 0 (initial) | 'B8(h)' of the frame sync-byte value is changed to '47(h)' inversely.                                                            |

|          |                    | 1           | 'B8(h)' of the frame sync-byte value is not changed.                                                                             |

| bit6     | Reserved           | 0 (initial) | Don't change.                                                                                                                    |

| MOD7     | Data reverse       | 0 (initial) | Normal operation.                                                                                                                |

|          | switch             | 1           | Received data is reversed in LSI.                                                                                                |

[MOD0 function]

#### MOD0 = 0

MOD0 = 1

#### (Continued)

#### [MOD1 function]

#### The structure of the transport packet

#### [MOD5 function]

#### MOD5 = 0

#### MOD5 = 1

#### 2. MODE-2

- Deinterleaver, Reed-Solomon and Energy dispersal removal functions may be passed through by setting the register.

- Register value: I<sup>2</sup>C address = 0001ADR [2:0], Register address = 00000001 (2) = 1 (10)

| Bit name | Function                    | Bit value   | Operation                                                |

|----------|-----------------------------|-------------|----------------------------------------------------------|

| DI_EN    | Deinterleaver               | 0           | Deinterleaver is not performed.                          |

|          | enable                      | 1 (initial) | Normal operation. Deinterleaver is performed.            |

| RS_EN    | Reed-Solomon                | 0           | Read-Solomon decoder is not performed.                   |

|          | enable                      | 1 (initial) | Normal operation. Reed-Solomon decoder is performed.     |

| ER_EN    | Energy                      | 0           | Energy dispersal removal is not performed.               |

|          | dispersal<br>removal enable | 1 (initial) | Normal operation. Energy dispersal removal is performed. |

- BCLK output may be changed by setting the register.

- Register value: I<sup>2</sup>C address = 0001ADR [2:0], Register address = 00000001 (2) = 1 (10)

| Bit name | Function    | Bit value    | Operation                                  |

|----------|-------------|--------------|--------------------------------------------|

| BCLK     | BCLK output | 00 (initial) | 'L' level output.                          |

| [1:0]    | select      | 01           | Packet start signal output.                |

|          |             | 10           | Clock of $2 \times$ symbol rate is output. |

|          |             | 11           | The same clock as symbol rate is output.   |

- It is prohibited to change the bit 5 to bit 7.

- Register value: I<sup>2</sup>C address = 0001ADR [2:0], Register address = 00000001 (2) = 1 (10)

| Bit name | Function | Bit value   | Operation     |

|----------|----------|-------------|---------------|

| bit 5    | Reserved | 0 (initial) | Don't change. |

| bit 6    |          | 0 (initial) | Don't change. |

| bit 7    |          | 0 (initial) | Don't change. |

#### 3. Status

- User can monitor the internal status.

- Register value: I<sup>2</sup>C address = 0001ADR [2:0], Register address = 00001001 (2) = 9 (10), Read only

| Bit name  | Function                          | Bit value | Operation                                              |

|-----------|-----------------------------------|-----------|--------------------------------------------------------|

| STA0      | Frame                             | 0         | It shows Frame isn't in synchronization.               |

|           | synchronization                   | 1         | It shows Frame is in synchronization.                  |

| STA1      | Viterbi decode<br>synchronization | 0         | It shows the Viterbi decoder isn't in synchronization. |

|           |                                   | 1         | It shows the Viterbi decoder is in synchronization.    |

| STA [4:2] | Viterbi rate                      | 000       | It shows the Viterbi decoder isn't in synchronization. |

|           | detection                         | 001       | It shows the Viterbi rate is 1/2.                      |

|           |                                   | 010       | It shows the Viterbi rate is 2/3.                      |

|           |                                   | 011       | It shows the Viterbi rate is 3/4.                      |

|           |                                   | 100       | It shows the Viterbi rate is 5/6.                      |

|           |                                   | 101       | It shows the Viterbi rate is 7/8.                      |

#### 4. A/D converter

• I and Q analog input data are automatically sampled by the internal clock.

#### 5. Nyquist filter

• Digital half Nyquist filtering is done for each I and Q input signal. The roll-off factor is 0.35.

#### 6. AGC

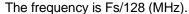

- The amplitude of I and Q input data is compared with the reference value AGC [4:0] set by the register. The compared result is output to AGC pin by the PWM (Pulse Width Modulation) form or 'H/L' level. It adjusts the amplifier gain of the tuner via the external analog filter.

- The pulse width of the PWM output is changed at 1/(2Fs) × n (μs) step (n=0 to 255, Fs: symbol rate (Msymbol/s)). The frequency is Fs/128 (MHz).

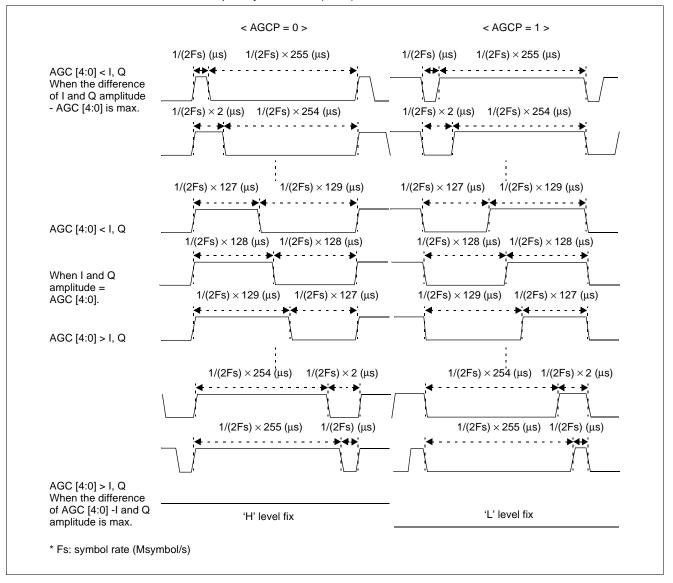

- The pulse width of the 'H/L' level output is changed at minimum 4/Fs (μs) step (Fs: symbol rate (Msymbol/s)). The frequency is maximum Fs/4 (MHz). As the response is rapider than PWM, it is useful to a quick response request.

- The reference value AGC [4:0] and the AGC output polarity are programmable.

- Register value: I<sup>2</sup>C address = 0001ADR [2:0], Register address = 00000010 (2) = 2 (10)

| Bit name  | Function               | Bit value          | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGC [4:0] | Reference value        | 00000              | Minimum reference value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|           | for AGC                | to                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           |                        | 10000<br>(initial) | The amplifier gain of the tuner is adjusted to equal to the reference value.                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |                        | to                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           |                        | 11111              | Maximum reference value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AGCM      | AGC output             | 0 (initial)        | PWM output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           | mode                   | 1                  | 'H/L' level output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AGCP      | AGC output<br>polarity | 0 (initial)        | <ul> <li>When AGC [4:0] &gt; Amplitude of I and Q input data:</li> <li>When AGCM = 0 (PWM output), it repeatedly outputs the pulse that 'H' period is longer than 'L' period.</li> <li>When AGCM = 1 ('H/L' level output), it outputs 'H'.</li> <li>When AGC [4:0] &lt; Amplitude of I and Q input data:</li> <li>When AGCM = 0 (PWM output), it repeatedly outputs the pulse that 'L' period is longer than 'H' period.</li> <li>When AGCM = 1 ('H/L' level output), it outputs 'L'.</li> </ul> |

|           |                        | 1                  | <ul> <li>When AGC [4:0] &gt; Amplitude of I and Q input data:</li> <li>When AGCM = 0 (PWM output), it repeatedly outputs the pulse that 'L' period is longer than 'H' period.</li> <li>When AGCM = 1 ('H/L' level output), it outputs 'L'.</li> <li>When AGC [4:0] &lt; Amplitude of I and Q input data:</li> <li>When AGCM = 0 (PWM output), it repeatedly outputs the pulse that 'H' period is longer than 'L' period.</li> <li>When AGCM = 1 ('H/L' level output), it outputs 'H'.</li> </ul> |

| bit 7     | Reserved               | 0 (initial)        | Do not set this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

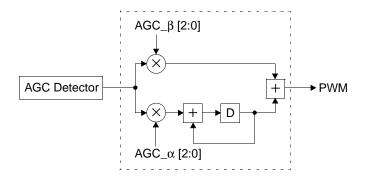

• Some external AGC-loop configuration in user systems may need to adjust the filter value using the following register.

| Bit name       | Function                       | Bit value        | Operation                  |

|----------------|--------------------------------|------------------|----------------------------|

| AGC_α          |                                | 000              | $\alpha = 2^{\circ} (= 1)$ |

| [2:0]          | of AGC loop-<br>filter         | 001              | $\alpha = 2^1 (= 2)$       |

|                |                                | 010              | $\alpha = 2^2 (= 4)$       |

|                |                                | 011<br>(default) | $\alpha = 2^3 (= 8)$       |

|                |                                | 100              | $\alpha = 2^4$ (= 16)      |

|                |                                | 101              | $\alpha = 2^5 (= 32)$      |

|                |                                | 110              | $\alpha = 2^{6} (= 64)$    |

|                |                                | 111              | —                          |

| AGC_β<br>[2:0] | β-Coefficiency<br>of AGC loop- | 000<br>(default) | $\beta = 0$                |

|                | filter                         | 001              | $\beta = 2^1 (= 2)$        |

|                |                                | 010              | $\beta = 2^2 (= 4)$        |

|                |                                | 011              | $\beta = 2^3 (= 8)$        |

|                |                                | 100              | $\beta = 2^4 (= 16)$       |

|                |                                | 101              | $\beta = 2^5 (= 32)$       |

|                |                                | 110              | $\beta = 2^6 (= 64)$       |

|                |                                | 111              | $\beta = 2^7 (= 128)$      |

• Register value: I<sup>2</sup>C address = 0001ADR [2:0], Register address = 00010011 (2) = 19 (10)

Block Diagram of AGC:

PWM AGC output wave form: The pulse width is changed at  $1/(2Fs) \times n$  (µs) step (n = 0 to 255, Fs: symbol rate (Msymbol/s).

#### (Continued)

'H/L' level AGC output wave form: The pulse width is changed at minimum 4/Fs ( $\mu$ s) step (Fs: symbol rate) The frequency is Fs/8 (MHz)

on

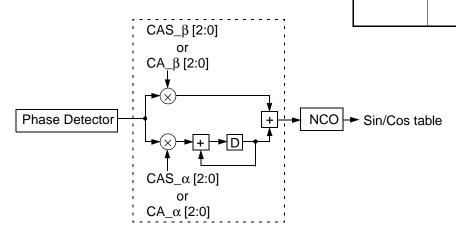

#### 7. Carrier recovery

- The difference of the carrier recovery in the tuner is automatically recovered up to ±5 MHz in the LSI.

- The loop filter coefficient for the carrier recovery operates with CAS\_ $\alpha$  [2:0] and CAS\_ $\beta$  [2:0] at first and then automatically switches to CA\_ $\alpha$  [2:0] and CA\_ $\beta$  [2:0] after the lock-up. However, when CA\_SW is "0", the filter coefficient always operates with CA\_ $\alpha$  [2:0] and CA\_ $\beta$  [2:0].

<Register address = 00000110(2) = 6(10)>

- The loop filter is variable.

- Register value: I<sup>2</sup>C address = 0001ADR [2:0]

| Bit name       | Function                     | Bit value     | Operation                             | Bit name      | Function                     | Bit value     | Operation                    |

|----------------|------------------------------|---------------|---------------------------------------|---------------|------------------------------|---------------|------------------------------|

| CAS_α          | α-factor                     | 000           | $\alpha = 2^{1}$ (=2)                 | CA_α          | α-factor                     | 000           | $\alpha = 2^{1}$ (=2)        |

| [2:0]          | for the loop filter at first | 001           | $\alpha = 2^2$ (=4)                   | [2:0]         | for the loop<br>filter after | 001 (initial) | $\alpha = 2^2$ (=4)          |

|                |                              | 010           | $\alpha = 2^3$ (=8)                   |               | lock-up                      | 010           | α = 2 <sup>3</sup> (=8)      |

|                |                              | 011 (initial) | α = 2 <sup>4</sup><br>(=16)           |               |                              | 011           | α = 2 <sup>4</sup><br>(=16)  |

|                |                              | 100           | $\alpha = 2^5$<br>(=32)               |               |                              | 100           | $\alpha = 2^5$<br>(=32)      |

|                |                              | 101 to 111    | $\alpha = 2^{6}$<br>(=64)             |               |                              | 101 to 111    | $\alpha = 2^{6}$<br>(=64)    |

| CAS_β<br>[2:0] | $\beta$ -factor for the loop | 000           | $\beta = 2^8$<br>(=256)               | CA_β<br>[2:0] | $\beta$ -factor for the loop | 000           | $\beta = 2^8$<br>(=256)      |

|                | filter at first              | 001           | β = 2 <sup>9</sup><br>(=512)          |               | filter after<br>lock-up      | 001           | β = 2 <sup>9</sup><br>(=512) |

|                |                              | 010           | $\beta = 2^{10}$<br>(=1024)           |               |                              | 010 (initial) | $\beta = 2^{10}$<br>(=1024)  |

|                |                              | 011 (initial) | $\beta = 2^{11}$<br>(=2048)           |               |                              | 011           | $\beta = 2^{11}$<br>(=2048)  |

|                |                              | 100           | $\beta = 2^{12}$<br>(=4096)           |               |                              | 100           | $\beta = 2^{12}$<br>(=4096)  |

|                |                              | 101 to 111    | $\beta = 2^{13}$<br>(=8192)           |               |                              | 101           | $\beta = 2^{13}$<br>(=8192)  |

| Carrier Rec    | overy Block Di               | agram.        | · · · · · · · · · · · · · · · · · · · | CA_SW         | Loop filter<br>SW            | 0             | Auto SW:<br>off              |

|                |                              | agiann        |                                       |               |                              | 1(initial)    | Auto SW:                     |

<Register address = 00010001(2) = 17(10)>

#### 8. AFC

- User can monitor the difference of the local oscillator frequency in the tuner.

- The different frequency of the tuner may be calculated by the following way by reading the register of AFC [7:0].  $\Delta f (KHz) = (128 - AFC [7:0]) \times 82.474 \times (n/42.192)$  (n: Receiving bit rate (Mbps))

- Ex.1: When AFC [7:0] = 01111100 and Receiving bit rate n = 40 (Mbps),

AFC (DEC) =  $2^2 + 2^3 + 2^4 + 2^5 + 2^6 = 124$

$\Delta f$  = 312.8 (KHz)  $\rightarrow$  It shows the local oscillator frequency in the tuner is 312.8KHz higher.

Ex.2: When AFC [7:0] = 10000101 and Receiving bit rate n = 60 (Mbps),

AFC (DEC) =  $2^0 + 2^2 + 2^7 = 133$

- $\Delta f$ = -586.4(KHz)  $\rightarrow$  It shows the local oscillator frequency in the tuner is 586.4KHz lower.

- Register value: I<sup>2</sup>C address = 0001ADR [2:0], Register address = 00001010 (2), Read only

| Bit name  | Function                    | Bit value | Operation                                                           |

|-----------|-----------------------------|-----------|---------------------------------------------------------------------|

| AFC [7:0] | The difference              | 00000000  | It shows the local oscillator frequency in the tuner is very high.  |

|           | of the carrier<br>frequency | 00000001  |                                                                     |

|           |                             | to        |                                                                     |

|           |                             | 01111111  |                                                                     |

|           |                             | 10000000  | It shows the local oscillator frequency in the tuner is almost fit. |

|           |                             | 10000001  |                                                                     |

|           |                             | to        |                                                                     |

|           |                             | 11111110  |                                                                     |

|           |                             | 111111111 | It shows the local oscillator frequency in the tuner is very low.   |

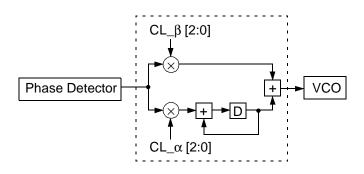

#### 9. Clock recovery

- The clock synchronized to the base band data is automatically recovered in the LSI. The internal VCO must be set to the required frequency in advance. Refer to '10. VCO' for setting the internal VCO frequency.

- The Loop filter is variable.

- Register value: I<sup>2</sup>C address = 0001ADR [2:0], Register address = 00000111(2) = 7(10)

| Bit name | Function                      | Bit value        | Operation                   |

|----------|-------------------------------|------------------|-----------------------------|

| CL_α     |                               | 000              | $\alpha = 2^9$ (=512)       |

| [2:0]    | clock recovery<br>loop filter | 001              | $\alpha = 2^{10} (=1024)$   |

|          |                               | 010<br>(initial) | $\alpha = 2^{11} (=2048)$   |

|          |                               | 011              | $\alpha = 2^{12} (=4096)$   |

|          |                               | 100              | $\alpha = 2^{13} (=8192)$   |

|          |                               | 101              | $\alpha = 2^{14} (=16384)$  |

|          |                               | 110, 111         | Prohibited                  |

| CL_β     | β-factor for the              | 000              | $\beta = 2^{17} (= 131072)$ |

| [2:0]    | clock recovery<br>loop filter | 001              | $\beta = 2^{18} (= 262144)$ |

|          |                               | 010              | $\beta = 2^{19} (=524288)$  |

|          |                               | 011<br>(initial) | $\beta = 2^{20} (=1048576)$ |

|          |                               | 100              | $\beta = 2^{21}$ (=2097152) |

|          |                               | 101              | $\beta = 2^{22} (=4194304)$ |

|          |                               | 110, 111         | Prohibited                  |

Clock Recovery Block Diagram:

#### 10. VCO

- The internal VCO frequency must be set to two times of the received data symbol rate. Because the frequency step is every 0.1 MHz step, set the nearest frequency.

- E.X.: When the received data symbol rate is 21.096 Msym/s, set 42.2 MHz as 21.096 Msym/s x2 = 42.192 MHz

- Register value: I<sup>2</sup>C adress = 0001ADR [2:0], Register address = 00000011(2) = 3(10) & 00000100(2) = 4(10)

| <b>Bit nome</b> | Function                                      | Bit value       | Operation                                                |                     |  |

|-----------------|-----------------------------------------------|-----------------|----------------------------------------------------------|---------------------|--|

| Bit name        | Function                                      | Dit value       | LVCO register = '0'                                      | LVCO register = '1' |  |

| VCO             | VCO Freq.                                     | 00000000        | Internal VCO is set to 40.0 MHz.                         |                     |  |

| [7:0]           | (0.1 MHz step)                                | 00000001        | Internal VCO is set to 40.1 MHz.                         |                     |  |

|                 |                                               | to              | to                                                       |                     |  |

|                 |                                               | 00000110        | Internal VCO is set to 40.6 MHz.                         |                     |  |

|                 |                                               | to              | to                                                       |                     |  |

|                 |                                               | 00010110        | Internal VCO is set to <b>42.2 MHz</b> . (Initial value) |                     |  |

|                 |                                               | to              | to                                                       |                     |  |

|                 |                                               | 01000100        | Internal VCO is set to 46.8 MHz.                         |                     |  |

|                 |                                               | to              | to                                                       |                     |  |

|                 |                                               | 01110100        | Internal VCO is set to <b>51.6 MHz</b> .                 |                     |  |

|                 |                                               | to              | to                                                       |                     |  |

|                 |                                               | 10010110        | Internal VCO is set to 55.0 MHz.                         |                     |  |

|                 |                                               | to              | to                                                       |                     |  |

|                 |                                               | 10100010        | Internal VCO is set to 56.2 MHz.                         |                     |  |

|                 |                                               | to              | to                                                       |                     |  |

|                 |                                               | 11001000        | Internal VCO is set to 60.0 MHz.                         |                     |  |

|                 |                                               | to              | to                                                       |                     |  |

|                 | 11011000 Internal VCO is set to 61.6 MHz. Set | Set to 36.0 MHz |                                                          |                     |  |

|                 |                                               | to to           | to                                                       |                     |  |

|                 |                                               | 11100000        | Internal VCO is set to 62.4 MHz.                         | Set to 36.8 MHz     |  |

|                 |                                               | to              | to                                                       | to                  |  |

|                 |                                               | 11111110        | Internal VCO is set to 65.4 MHz.                         | Set to 39.8 MHz     |  |

|                 |                                               | 11111111        | Internal VCO is set to 65.5 MHz.                         | Set to 39.9 MHz     |  |

#### 11. RESET

- The whole block of LSI or QPSK-Block only is reset when LSI\_RST or QP\_RST bit is set to '1'.

- Register value: I<sup>2</sup>C address = 0001ADR [2:0], Register address = 00001000 (2) = 8(10)

| Bit name | Function                              | Bit value | Operation                                                 |

|----------|---------------------------------------|-----------|-----------------------------------------------------------|

| LSI_RST  | The whole of<br>LSI<br>Software reset | 1         | The whole of LSI is reset when LSI_RST bit is set to '1'. |

| QP_RST   | QPSK Block<br>Software reset          | 1         | QPSK-Block only is reset when QP_RST bit is set to '1'.   |

#### 12. Viterbi decoder

- Constraint length K = 7.

- Optionally some Viterbi rates may be selected from R = 1/2, 2/3, 3/4, 5/6 and 7/8.

- The receiving Viterbi rate is automatically detected from some selected Viterbi rates. It is getting longer to detect it in proportion to the number of selected rates. So it is recommended to select one rate, if the rate is known beforehand.

- The detected Viterbi rate is written to the STA [4:2] register which is shown in '3. Status'.

- Register value: I<sup>2</sup>C address = 0001ADR [2:0], Register address = 00000100 (2) = 4(10)

| Bit name | Function        | Bit value   | Operation                                               |

|----------|-----------------|-------------|---------------------------------------------------------|

| VIR0     | R = 1/2 setting | 0 (initial) | Viterbi rate detection is not performed for $R = 1/2$ . |

|          |                 | 1           | Viterbi rate detection is performed for $R = 1/2$ .     |

| VIR1     | R = 2/3 setting | 0 (initial) | Viterbi rate detection is not performed for $R = 2/3$ . |

|          |                 | 1           | Viterbi rate detection is performed for $R = 2/3$ .     |

| VIR2     | R = 3/4 setting | 0           | Viterbi rate detection is not performed for $R = 3/4$ . |

|          |                 | 1 (initial) | Viterbi rate detection is performed for $R = 3/4$ .     |

| VIR3     | R = 5/6 setting | 0 (initial) | Viterbi rate detection is not performed for $R = 5/6$ . |

|          |                 | 1           | Viterbi rate detection is performed for $R = 5/6$ .     |

| VIR4     | R = 7/8 setting | 0 (initial) | Viterbi rate detection is not performed for $R = 7/8$ . |

|          |                 | 1           | Viterbi rate detection is performed for $R = 7/8$ .     |

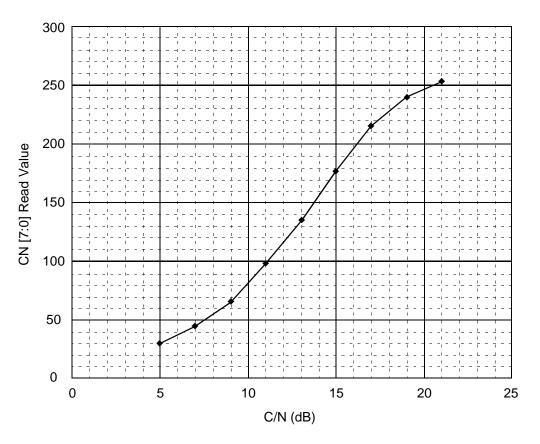

#### 13. C/N monitor

- The approximate C/N value of the LSI input is monitored.

- The monitored C/N value depends on evaluation circumstance, LSI mounting conditions, and so on in user application system. Therefore, the value must be carefully checked before user's finished product. The typical characteristic curve is shown in below.

- Register value: I<sup>2</sup>C address = 0001ADR [2:0], Register address = 00001011 (2) = 11(10), Read only

| Bit name | Function    | Bit value | Operation                                          |

|----------|-------------|-----------|----------------------------------------------------|

| CN [7:0] | C/N monitor | 00000000  | It shows the error of the receiving data is large. |

|          |             | to        |                                                    |

|          |             | 11111111  | It shows the error of the receiving data is small. |

Note: CN [7:0] Read Value is transferred to the decimal value.

#### 14. Frame synchronization

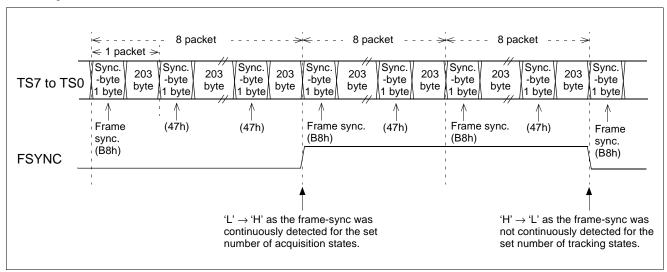

- The frame synchronization signal (B8h) on the head of 8 packets is detected. The number of states for acquisition and tracking is programmable.

- The LSI is judged to lock if the synchronization signal would be continuously detected for the set number of acquisition states, and then FSYNC is changing to 'H' (when MOD4 (Register address: 0000000) = '0'). After lock, the LSI is judged not to lock if the synchronization signal would not be continuously detected for the set number of tracking states, and then FSYNC is changing to 'L'.

- Register value: I<sup>2</sup>C address = 0001ADR [2:0], Register address = 00000101 (2) = 5(10)

| Bit name  | Function              | Bit value                    | Operation                                                                                                     |

|-----------|-----------------------|------------------------------|---------------------------------------------------------------------------------------------------------------|

| SYA [3:0] | Number of acquisition | 0000,0001,<br>0010 (initial) | The LSI is judged to lock if the synchronization signal would be continuously detected two times.             |

|           | states                | to                           |                                                                                                               |

|           |                       | 1111                         | The LSI is judged to lock if the synchronization signal would be continuously detected fifteen times.         |

| SYT [3:0] | Number of tracking    | 0000 to 0010                 | The LSI is judged not to lock if the synchronization signal would not be continuously detected two times.     |

|           | states                | to                           |                                                                                                               |

|           |                       | 1111 (initial)               | The LSI is judged not to lock if the synchronization signal would not be continuously detected fifteen times. |

#### Timing

#### 15. Deinterleaver

- The deinterleaving depth I = 12 on byte-stream.

- When DI\_EN (Register address =00000001) = '0', Deinterleaver is not performed. When DI\_EN = '1', Deinterleaver is performed.

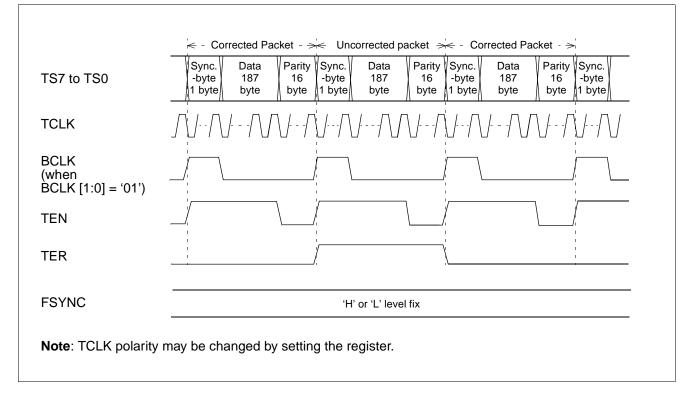

#### 16. Reed-Solomon decoder

- n = 204, k = 188, t = 8 Code Generator Polynomial: g (x) = (x +  $\lambda^0$ ) (x +  $\lambda^1$ ) (x +  $\lambda^2$ ) · · · (x +  $\lambda^{15}$ ) Field Generator Polynomial: p (x) = x<sup>8</sup> + x<sup>4</sup> + x<sup>3</sup> + x<sup>2</sup> + 1

- If the total errors are less than 8 bytes at 204 bytes unit, all errors can be corrected. If the total errors are more than 9 bytes, all errors are not corrected. The TER outputs 'L' for a packet that all errors were corrected. The TER outputs 'H' for a packet that the errors were not corrected.

- To distinguish the parity bytes of Reed-Solomon, the TEN outputs 'H' for a period of the valid data, and then outputs 'L' for a period of the parity bytes.

- When RS\_EN (Register address: 00000001) = '0', Reed-Solomon decoder is not performed and all errors are not corrected. TEN operates normally, but TER outputs 'L'.

When RS\_EN = '1', Reed-Solomon decoder is performed.

|                          | < - Corrected Packet - >< Uncorrected packet >< - Corrected Packet - >                                              |

|--------------------------|---------------------------------------------------------------------------------------------------------------------|

| TS7 to TS0               | Sync.DataParitySync.DataParitySync.Data-byte18716-byte18716-byte187161 bytebyte1 bytebyte1 bytebyte1 bytebyte1 byte |

| TCLK                     |                                                                                                                     |

| TEN                      |                                                                                                                     |

| TER<br>(when RSEN = '1') |                                                                                                                     |

| TER<br>(when RSEN = '0') | 'L' level fix                                                                                                       |

#### Timing

#### 17. Energy dispersal removal

- When ER\_EN (Register address: 00000001) = '0', Energy dispersal removal is not performed. When ER\_EN = '1', Energy dispersal removal is performed.

- Pseudo Random Binary Sequence (PRBS) Polynomial: x<sup>15</sup> + x<sup>14</sup> + 1 The polynomial is initialized into the sequence '100101010000000' every eight packets.

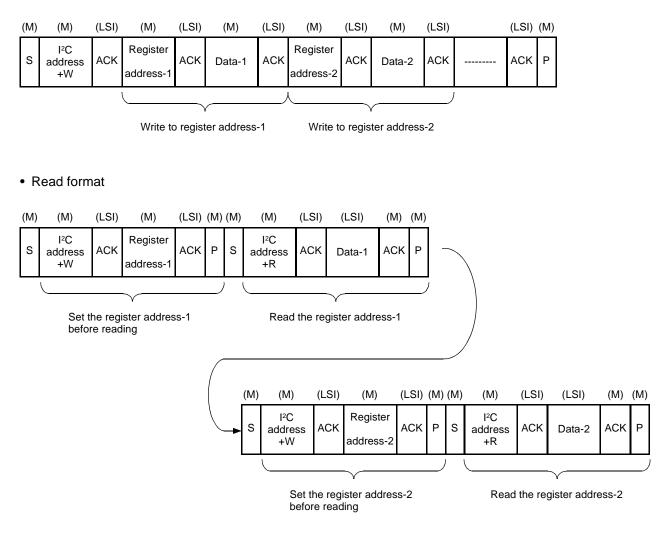

#### 18. I<sup>2</sup>C bus

• Write format

Note: S: Start condition

I<sup>2</sup>C address (7bit): 0001 (ADR2) (ADR1) (ADR0) ADR [2:0]: user setting R/W (1bit): 0 = write, 1 = read Data-n (8bit): Data of register address-n ACK: Acknowledge P: Stop condition (M) : Output signal of I<sup>2</sup>C master (LSI): Output signal of MB86660A

#### ■ OUTPUT SIGNAL TIMING

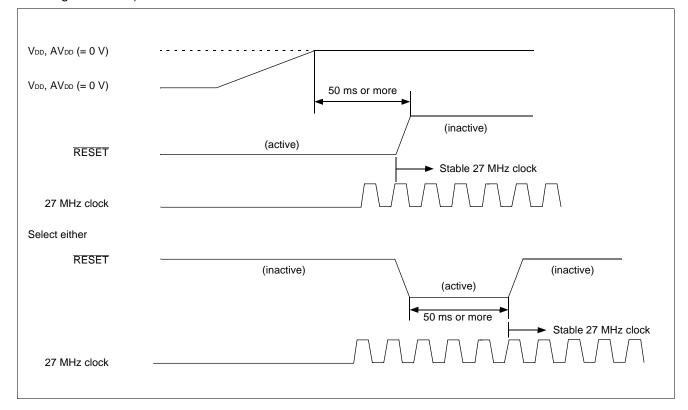

#### POWER-ON RESET

The MB86660A must be reset via RESET pin when the power is turned on.

Apply a reset signal to the LSI at power-on, then cancel the reset 50 ms after the V<sub>DD</sub> and AV<sub>DD</sub> have reached 3.3 V or input a reset pulse with a width of 50 ms after they reached 3.3 V. Note that the 27.0 MHz clock by the crystal oscillator or the external clock of EXTCLK must be stable before the reset is canceled. (See the diagram below.)

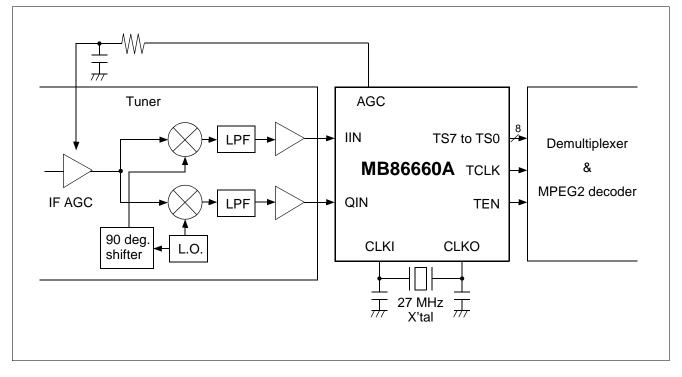

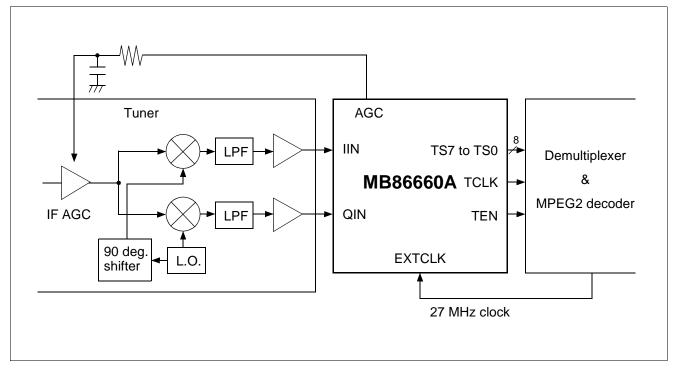

#### APPLICATION EXAMPLE

• When 27 MHz crystal oscillator is used.

• When 27 MHz external clock is used.

#### PERIPHERAL CIRCUIT EXAMPLE

- **Notes:** 1. The analog and digital power supplies should be separated and each GND pattern should be sufficient wide. Connect the bypass capacitors with good high frequency characteristics for V<sub>DD</sub> V<sub>SS</sub> and AV<sub>DD</sub> AV<sub>SS</sub>. Connect the analog and digital power supply pattern at a point such as the above illustration.

- Connect the bypass capacitors with good high frequency characteristics between the analog GND 'AVss' and VRHI, VRLI, VRHQ and VRLQ which are the reference voltage of A/Ds. It is most important to stabilize the reference voltage for A/D. Furthermore, it is recommended to connect a large value of about 10 μF to AVss.

- 3. Use the board with 4-layer or more.

### FUJITSU LIMITED

For further information please contact:

#### Japan

FUJITSU LIMITED Corporate Global Business Support Division Electronic Devices KAWASAKI PLANT, 4-1-1, Kamikodanaka Nakahara-ku, Kawasaki-shi Kanagawa 211-8588, Japan Tel: (044) 754-3763 Fax: (044) 754-3329

http://www.fujitsu.co.jp/

#### North and South America

FUJITSU MICROELECTRONICS, INC. Semiconductor Division 3545 North First Street San Jose, CA 95134-1804, USA Tel: (408) 922-9000 Fax: (408) 922-9179

Customer Response Center *Mon. - Fri.: 7 am - 5 pm (PST)* Tel: (800) 866-8608 Fax: (408) 922-9179

http://www.fujitsumicro.com/

#### Europe

FUJITSU MIKROELEKTRONIK GmbH Am Siebenstein 6-10 D-63303 Dreieich-Buchschlag Germany Tel: (06103) 690-0 Fax: (06103) 690-122

http://www.fujitsu-ede.com/

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE LTD #05-08, 151 Lorong Chuan New Tech Park Singapore 556741 Tel: (65) 281-0770 Fax: (65) 281-0220

http://www.fmap.com.sg/

F9802 © FUJITSU LIMITED Printed in Japan All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.). CAUTION:

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan.